— Surface Roughness and Application Analysis of Multi-wire Slicing, Grinding, and CMP Polishing

I. Characteristics and Processing Challenges of Silicon Carbide

Silicon carbide (SiC) is a

third-generation wide-bandgap semiconductor material known for its superior thermal, mechanical, and electrical properties. It is widely used in high-end applications such as new energy vehicles, rail transit, 5G communication, and aerospace.

| Property |

Typical Value

(4H-SiC, room temperature) |

Description |

| Mohs hardness |

9.2 – 9.3 |

Second only to diamond |

| Thermal conductivity |

490 W/m·K |

Excellent heat dissipation |

| Bandgap width |

3.26 eV |

Wide bandgap feature |

| Breakdown field |

2.8 MV/cm |

About 10× higher than silicon |

However, these same characteristics also bring extreme processing difficulties.

Summary:Due to its high hardness and chemical stability, SiC is far more difficult to process than silicon. This requires extremely precise control of process parameters and equipment performance.

II. SiC Substrate Processing Chain

The typical

SiC wafer processing sequence is:

Crystal growth → Orientation and rounding → Multi-wire slicing → Grinding → CMP polishing → Cleaning and inspectionEach subsequent step is designed to

remove the surface and subsurface damage caused by the previous process, gradually improving the surface quality to an atomically flat level.

III. Multi-Wire Slicing: Shaping and Initial Surface Formation

Principle

Multi-wire slicing uses a high-speed diamond wire to cut

SiC ingots into thin wafers.

Material removal occurs in the

brittle regime, where SiC fractures and chips due to its extreme hardness.

Surface Condition

Macroscopic: Clear cutting marks and directional textures.

Microscopic: Numerous microcracks, fractures, and pits. Damage depth can reach

10–20 μm.

Surface Roughness

Ra = 0.8 – 2.5 μm (800–2500 nm)

Application Analysis

Status: Sliced wafers cannot be used directly for device fabrication or epitaxy.

Purpose: To

shape the wafer and control thickness, providing material allowance for subsequent grinding.

IV. Grinding: Damage Removal and Surface Flattening

Principle

Grinding uses diamond slurry and a grinding plate to remove the damaged layer left by slicing.

This process marks the

transition from brittle to plastic material removal, though brittle mode still dominates.

Surface Condition

Macroscopic: Uniform matte appearance; cutting marks are removed.

Microscopic: Deep cracks are eliminated, but fine scratches and shallow grooves remain.

The new plastic damage layer is typically

2–5 μm deep.

Surface Roughness

Ra = 0.2 – 0.8 μm (200–800 nm)

Application Analysis

Purpose: To

remove slicing damage and improve flatness, preparing for CMP.

Status: A semi-finishing step — not suitable for high-end epitaxy.

Special case: Can be used for the

backside of power devices where surface requirements are lower.

V. CMP Polishing: Achieving Atomically Smooth, Damage-Free Surfaces

Principle

Chemical Mechanical Polishing (CMP) combines

chemical reactions and mechanical removal:

Chemical action: Alkaline slurry reacts with SiC to form a soft SiO₂ layer.

Mechanical action: Polishing pad and nanoscale abrasives remove this layer cyclically.

This process occurs mainly in the

plastic regime, introducing almost

no new mechanical damage.

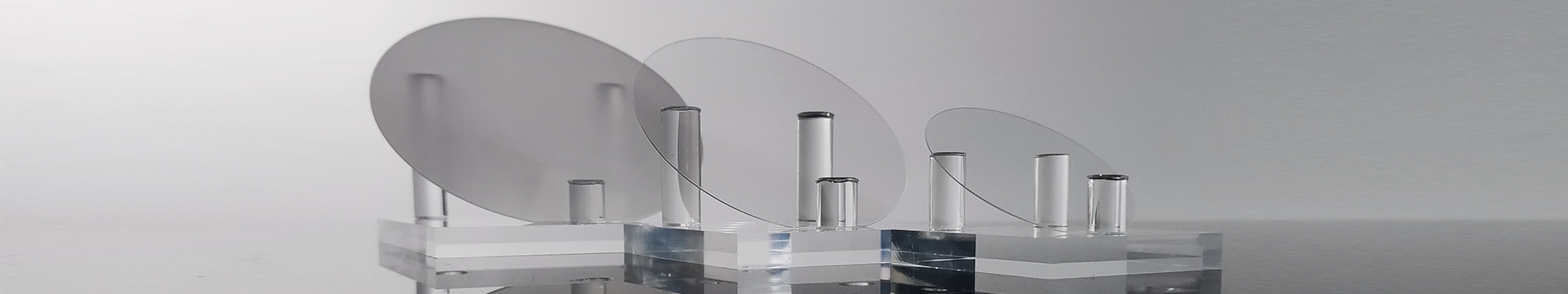

Surface Condition

Macroscopic: Mirror-like finish with clear reflections.

Microscopic: Atomic step-flow structures observed under AFM; no cracks or deformation layers.

Surface Roughness

Ra < 0.5 nm (premium products < 0.2 nm)

Application Analysis

Status: Final usable condition for high-end device manufacturing.

Applications:Power electronics (EVs, rail transit, smart grids)

RF devices (5G base stations, radar systems)

High-temperature electronics (aerospace, oil exploration)

LED substrates (for high-brightness GaN-based LEDs)

VI. Process Comparison and Performance Summary

| Process Stage |

Surface Description |

Roughness

(Ra) |

Damage Depth |

Main Function |

Application Status |

| Multi-wire slicing |

Visible cutting marks, microcracks |

0.8–2.5 μm |

10–20 μm |

Shaping and thickness control |

Requires further processing |

| Grinding |

Matte surface, uniform scratches |

0.2–0.8 μm |

2–5 μm |

Remove slicing damage |

Semi-finishing |

| CMP polishing |

Mirror surface, atomically smooth |

<0.5 nm |

None |

Achieve atomically flat surface |

Final usable state |

VII. Conclusion and Insights

The SiC substrate processing chain is essentially a

progressive refinement process, where each stage removes the damage from the previous one and reduces surface roughness step by step.

From multi-wire slicing to CMP, the process transforms the surface from a

brittle, damaged state to a

mirror-like, defect-free finish.

CMP polishing enables SiC substrates to reach atomic-level flatness and stability, providing the essential foundation for high-performance device fabrication.

Core Insight:

Core Insight:SiC substrate processing is not merely a competition of machining precision—it is an integration of

material science, process control, and surface engineering.

With continuous innovation in CMP chemistry and automation, the yield and efficiency of SiC substrates will keep improving, driving the rapid advancement of the third-generation semiconductor industry.